2. ЦИФРОВАЯ МИКРОЭЛЕКТРОНИКА ДЛЯ СИСТЕМ ЗАЩИТЫ И АВТОМАТИКИ

Булева алгебра и логические элементы

Математический аппарат, который используется для описания цифровых устройств, называется алгеброй логики или Булевой алгеброй по имени автора - английского математика Джорджа Буля (1815-1864 гг.).

Булева алгебра оперирует с двоичными переменными и с двоичными (или Булевыми) функциями.

Из таблицы истинности для этой функции следует:

0 + 0 = 0; 0+1 = 1; 1+0=1; 1 + 1 = 1.

Логические функции И, ИЛИ могут иметь любое количество аргументов.

Логическое отрицание является функцией только одной переменной (табл. 2.3). Она принимает единичное значение, если аргумент равен 0, и нулевое значение, если аргумент равен 1. Инверсию обозначают чертой над символом аргумента: у=х.

Из определения логического отрицания:

Функции И, ИЛИ, НЕ являются простейшими логическими операциями. На их основе строят логические выражения для описания других, более сложных функций. Наиболее часто используемые логические функции приведены в табл. 2.4. Следует отметить, что все операции Булевой алгебры дуальны. Например, конъюнкция для единиц является дизъюнкцией для нулей.

Таблица 2.4

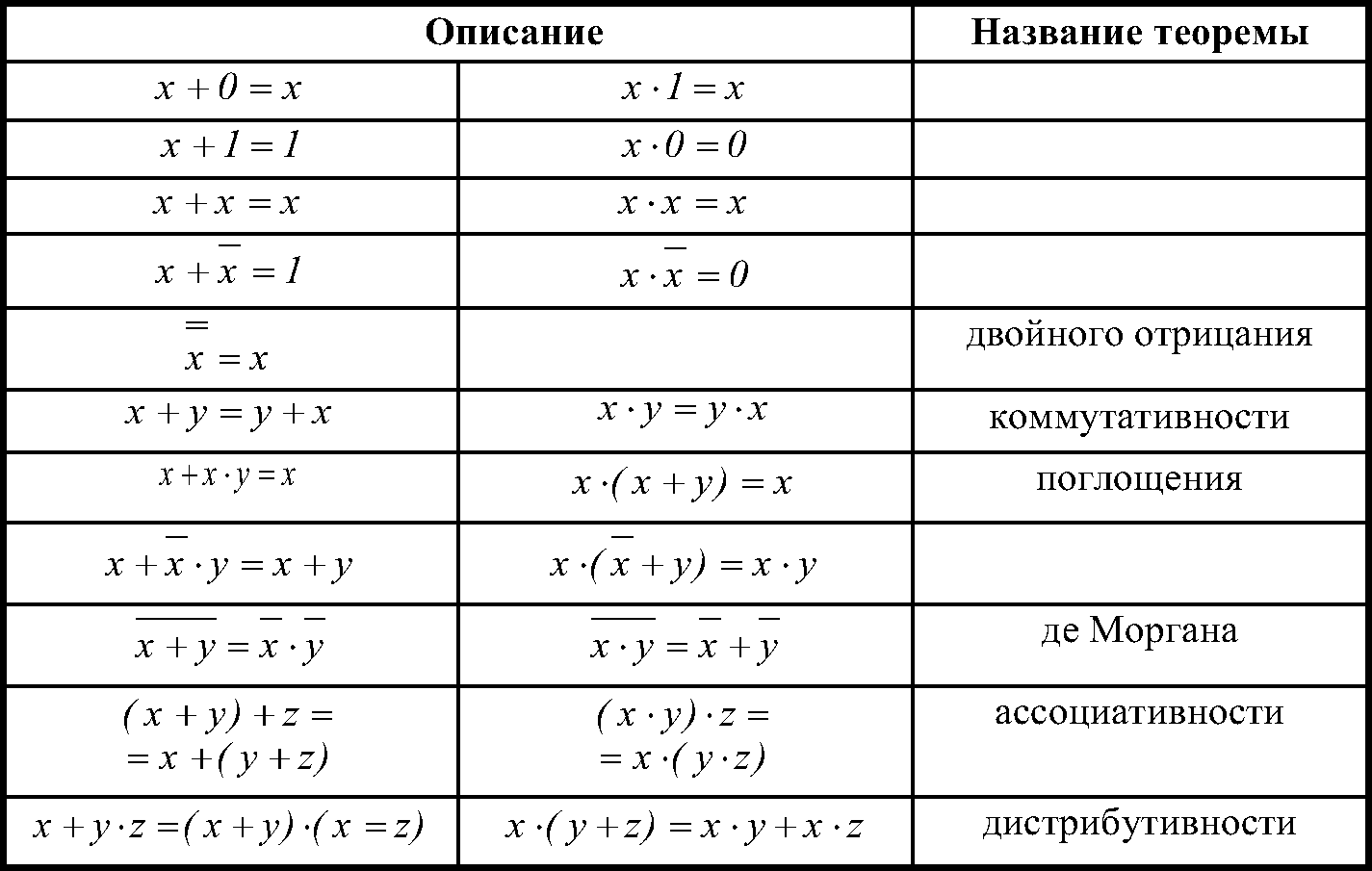

Из определений трех основных логических функций следуют теоремы Булевой алгебры, которые с учетом свойства дуальности сведены в табл.2.5. Они устанавливают основные соотношения алгебры логики и используются для преобразования логических выражений.

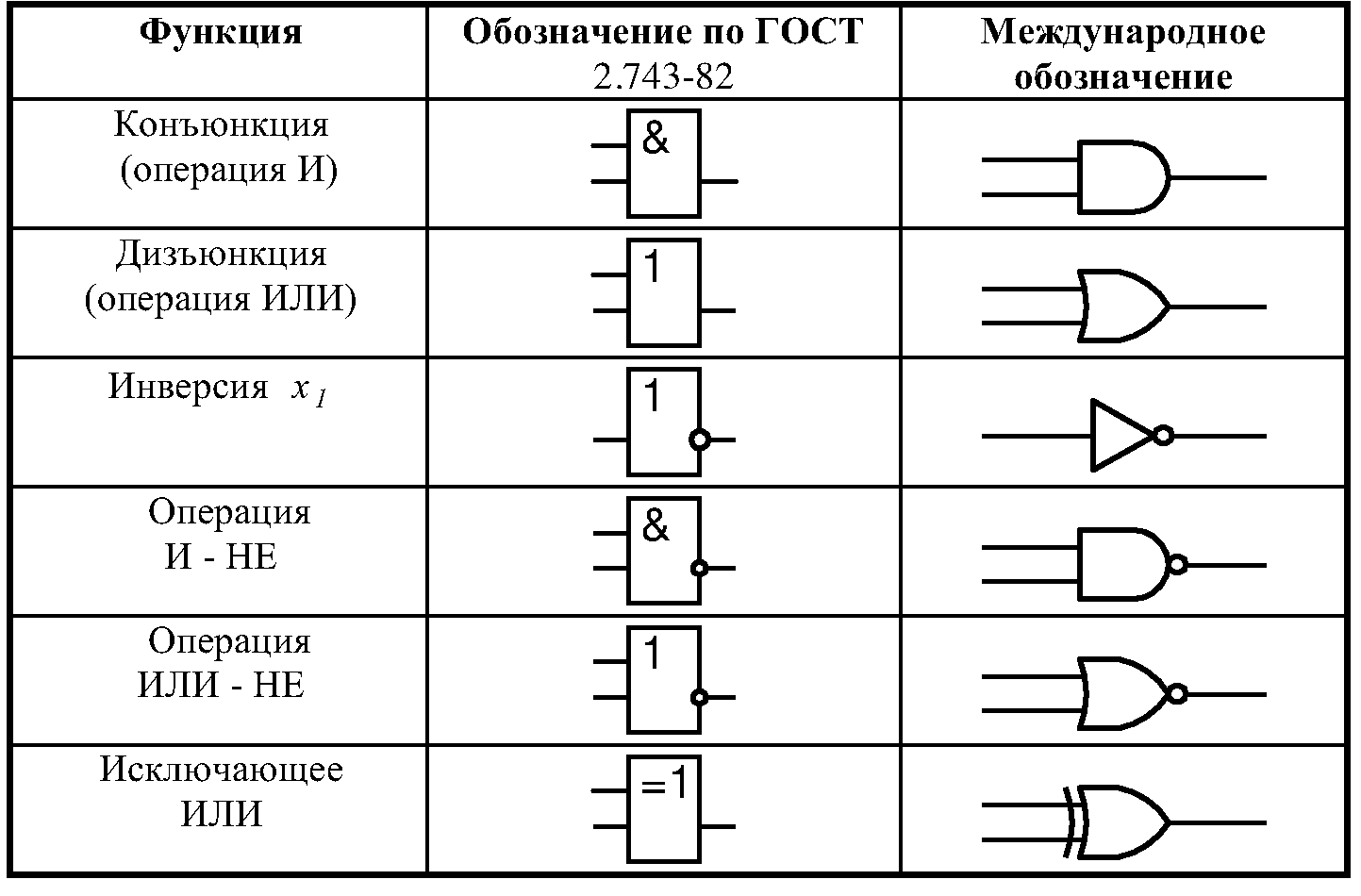

Полупроводниковые устройства, выполняющие в аппаратуре логические операции, называют логическими элементами. Логические элементы различаются между собой характером выполняемой функции, числом входов, числом выходов. Графическое обозначение логических элементов принятое в нашей стране и за рубежом, показано в таблице 2.6.

Функциональные цифровые узлы

На основе элементарных логических элементов (вентилей) строятся типовые функциональные узлы, которые, в свою очередь, являются основой более сложных цифровых систем.

Наиболее простые функциональные узлы (селекторы, дешифраторы), которые не обладают свойством памяти, называются комбинационными цепями. Состояние выходных сигналов в каждый момент времени у них определяется состоянием входных сигналов.

Таблица 2.6

Функциональные узлы, обладающие памятью (триггеры, регистры, счетчики, запоминающие устройства), называются последовательностными цепями. Их состояние определяется не только текущим значением входных сигналов, но и их значениями в предшествующие моменты времени.

Триггеры

Триггер - это логический функциональный элемент, который может находиться в одном из двух устойчивых состояний и обладает свойством памяти.

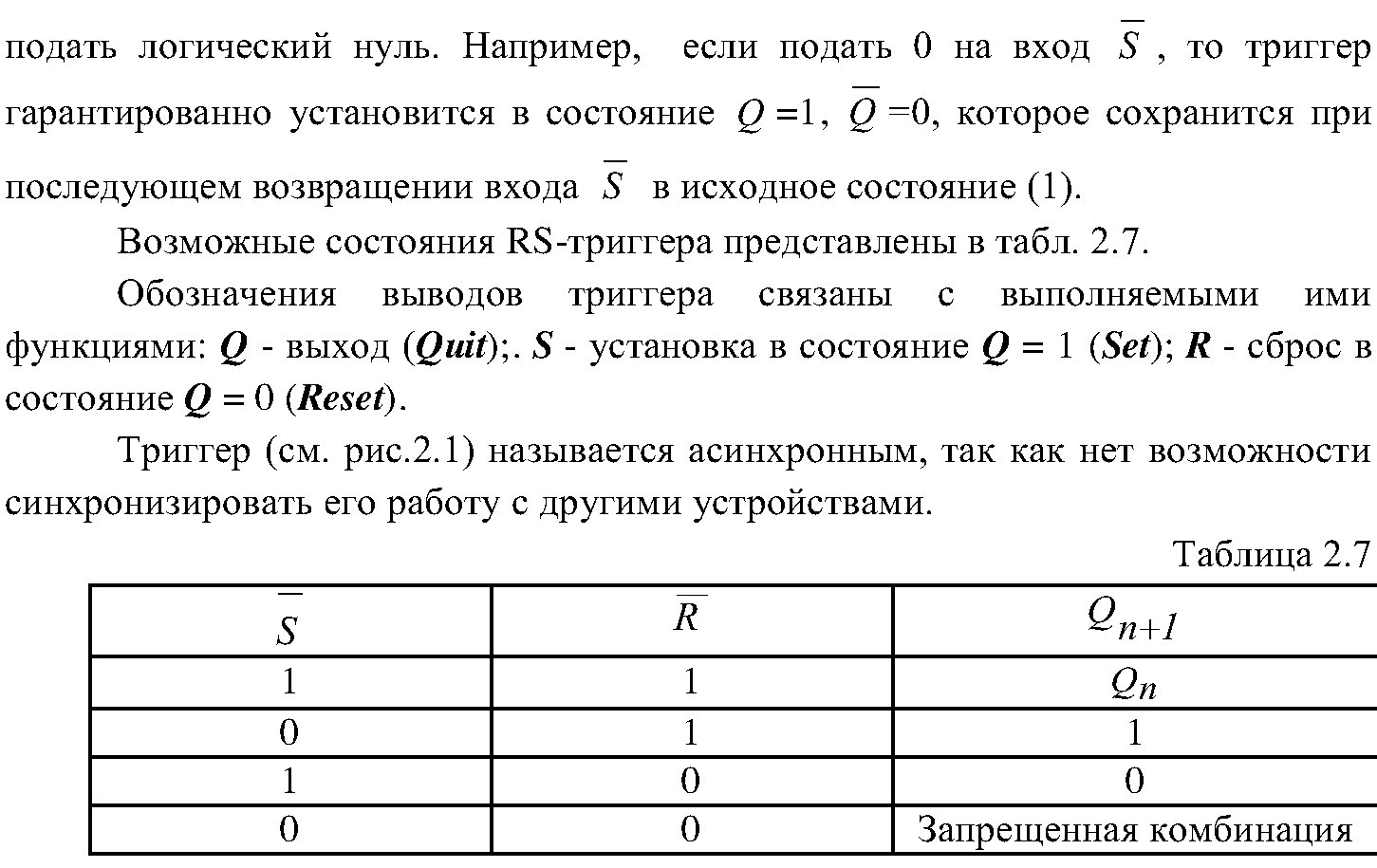

Если на обоих входах простейшего RS-триггера (рис.2.1) присутствуют логические единицы, то он находится в режиме хранения информации.

Рис. 2.1

Для того, чтобы изменить его состояние достаточно на один из входов кратковременно

В синхронном (тактируемом) триггере (рис. 2.2) изменение состояния происходит только при наличии разрешающего сигнала на синхронизирующем (тактовом) входе (С).

Тактирование может осуществляться импульсом (потенциалом) или фронтом импульса (перепадом потенциала).

Тактируемый потенциалом триггер (см. рис. 2.2,а) блокируется, когда синхронизирующий сигнал на входе С равен 0. Когда на синхронизирующий вход подана логическая 1, триггер открыт, и изменение входного сигнала приводит к изменению сигнала на выходе.

Графическое обозначение тактируемого потенциалом RS-триггера в интегральном исполнении см. на рис. 2.2,б.

Триггер, тактируемый фронтом, воспринимает входные воздействия только в момент перехода сигнала на тактовом входе в противоположное логическое состояние. Используют разные графические обозначения тактовых входов для триггеров, срабатывающих по положительному (переход из нуля в единицу) перепаду тактового сигнала (см. рис. 2.2, в) и для триггеров, срабатывающих по отрицательному (переход из единицы в нуль) перепаду (см. рис. 2.2, г).

У D-триггера при разрешающем сигнале на тактовом входе логическое состояние с D-входа передается на выход Q. Тактирование D-триггера может осуществляться импульсом или фронтом.

Т -триггеры (или счетные триггеры) всегда тактируются фронтом. Если на информационном Т -входе присутствует 1, то тактовый импульс переводит триггер в противоположное состояние. Если на 7-входе 0, то триггер сохраняет предыдущее состояние. Если у Т -триггера отсутствует вход Т, то каждый очередной синхроимпульс переводит триггер в противоположное состояние.

Реальные интегральные микросхемы триггеров имеют дополнительные входы (см. рис. 2.3) для начальной установки ( S ) и сброса ( R ), которые могут быть синхронными и асинхронными.

Регистры

Регистр представляет собой группу триггеров, работающих согласованно и предназначенных для запоминания комбинации двоичных разрядов. Триггер используется здесь как элементарная ячейка памяти.

Тактирование всех триггеров, составляющих регистр, осуществляется по одному общему синхровходу. Поэтому, переключение состояний всех разрядов в регистре происходит одновременно (синхронно).

Существуют регистры с параллельной и последовательной записью информации. На рис.2.4 приведена структура регистра с параллельной записью.

Достаточно одного тактового импульса, чтобы двоичные данные со входов D0-D3 записались в параллельный регистр.

Регистры, тактируемые импульсом, получили название “фиксаторы” или “защелки”. Они отслеживают входные сигналы в открытом состоянии (при наличии разрешающего потенциала на синхровходе С) и хранят их последнее значение в закрытом.

Рис. 2.5

Выходы регистров часто объединяют параллельно общей шиной (рис. 2.5). При такой организации в каждый момент времени выставлять данные на шину разрешается только одному регистру. Другие регистры должны при этом отсоединить свои выводы от шины при помощи внутренних ключей по управляющему сигналу на входе![]() . Такое состояние выходов называется третьим состоянием (Ζ-состоянием). В регистре с последовательной записью информации (в регистре сдвига) триггеры соединены каскадно (выход предыдущего является входом

. Такое состояние выходов называется третьим состоянием (Ζ-состоянием). В регистре с последовательной записью информации (в регистре сдвига) триггеры соединены каскадно (выход предыдущего является входом

последующего). Вход первого триггера является информационным входом всего регистра (рис. 2.6).

Рис. 2.6

Данные, предназначенные для записи в регистр, подаются на его вход последовательно во времени (бит за битом). Эти данные сопровождаются тактовыми импульсами на синхровходе, который так же, как и у параллельных регистров, является общим для всех триггеров регистра. При поступлении очередного тактового импульса на синхровход комбинация “нулей” и “единиц” в регистре смещается на один разряд. Запись в последовательный регистр 8-разрядного двоичного числа выполняется за восемь сдвигов.

Регистры сдвига в интегральном исполнении кроме последовательной записи и считывания информации могут дополнительно обеспечивать параллельную запись и/или считывание. Такая организация позволяет использовать регистры сдвига для преобразования двоичных данных из параллельной формы в последовательную и наоборот.

Счетчики

Счетчик - это функциональный узел, предназначенный для подсчета количества импульсов, поступающих на его вход и состоящий, так же как и регистр, из отдельных триггеров. Комбинация логических состояний триггеров образует на выходе счетчика кодовую комбинацию, которая меняется при поступлении очередного счетного импульса. После того, как счетчик последовательно пройдет через все возможные состояния, он возвращается к первой кодовой комбинации, и счет повторяется.

Количество возможных кодовых комбинаций на выходе счетчика принято называть коэффициентом пересчета счетчика или его модулем.

Двоичные счетчики реализуют двоичную счетную последовательность, которая показана на временных диаграммах (рис. 2.7) и представлена в табл. 2.8.

Рис. 2.7

Значение разряда при поступлении очередного счетного импульса изменяется, если при этом все более младшие разряды имеют единичное значение.

Синхронные счетчики строят на Т-триггерах (рис.2.8), в которых на T-вход (вход разрешения перехода в противоположное состояние) каждого триггера подается конъюнкция логических состояний всех более младших разрядов. Счетный импульс поступает на синхровходы всех триггеров и одновременно переводит в противоположное состояние те из них, для которых сформирован разрешающий сигнал. Такие счетчики называются синхронными.

Таблица 2.8

Q3 | Q2 | Q1 | Q0 |

0 | 0 | 0 | 0 |

0 | 0 | 0 | 1 |

0 | 0 | 1 | 0 |

0 | 0 | 1 | 1 |

0 | 1 | 0 | 0 |

0 | 1 | 0 | 1 |

0 | 1 | 1 | 0 |

0 | 1 | 1 | 1 |

1 | 0 | 0 | 0 |

1 | 0 | 0 | 1 |

В асинхронных счетчиках триггеры меняют свое состояние не синхронно, а последовательно. В результате при поступлении очередного тактового импульса на выходах асинхронного счетчика в течении переходного процесса могут существовать ложные кодовые комбинации. Это необходимо учитывать при выборе счетчиков.

Рис. 2.8

В реверсивных счетчиках можно изменять направление счета. Они могут иметь два счетных входа (импульсы на одном увеличивают код счетчика, на другом - уменьшают) или один счетный вход и один управляющий вход, логический сигнал на котором задает направление счета.

Счетная последовательность десятичного счетчика зависит от способа представления десятичных чисел. Наиболее распространено представление в двоично-кодированном десятичном коде, в котором каждая десятичная цифра кодируется четырехразрядным двоичным числом. Десятичный счетчик использующий такое представление двоичного числа состоит из нескольких подсчетчиков (декадных счетчиков), соответствующих десятичным разрядам. Счетная последовательность суммирующего декадного счетчика в этом случае совпадает с двоичной последовательностью от 0000 до 1001, после чего следует снова 0000.