Аналого-цифровые преобразователи (АЦП) предназначены для преобразования аналоговых электрических сигналов в цифровой код и применяются для сопряжения устройств аналоговой и цифровой электроники [3,6]. Существуют АЦП мгновенных значений, которые осуществляют аналого-цифровое преобразование мгновенных значений выборок входного аналогового сигнала с заданным шагом дискретизации, и интегрирующие АЦП, выходной цифровой сигнал которых пропорционален интегральному значению входной аналоговой величины.

В устройствах контроля параметров и защиты преимущественно используются АЦП первой группы. Возможны три метода преобразования сигналов в АЦП этой группы: параллельный, весовой и числовой.

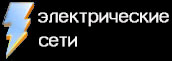

Структурная схема АЦП параллельного преобразования приведена на рис. 1.25. Устройство содержит источник опорного напряжения Uo; компараторы A1-An ; резистивный делитель напряжения с сопротивлениями R и (1/2) R ; регистр-дешифратор DC.

При параллельном способе построения АЦП преобразуемое напряжение UВХОД одновременно сравнивается с n-опорными напряжениями на инверсных входах компараторов А1-Ап , формируемых резистивным делителем. Выходной код АЦП получается в результате записи в регистр DC логического состояния компараторов А 1-Ап. Данный тип АЦП имеет максимальное быстродействие и не требует применения во входных цепях устройств выборки и хранения.

Их недостаток - высокие аппаратные затраты, высокое энергопотребление, следовательно, и высокая стоимость. Необходимое количество компараторов А1-Ап равно значению максимального десятичного выходного кода АЦП минус единица, при построении АЦП с разрядностью 8 бит необходимо 255 компараторов.

Выходной код АЦП определяется из выражения![]() , где

, где

п - количество компараторов А1-Ап или десятичное число, соответствующее максимальному значению выходного кода АЦП.

Современные интегральные технологии позволяют воспроизводить АЦП параллельного типа с разрядностью до 10 бит. Эти АЦП способны обрабатывать сигналы с частотой до 100 МГц.

Типовые характеристики интегральных параллельных АЦП приведены в табл. 1.3.

Таблица 1.3

Фирма изготовитель | Тип микросхемы | Разрядность АЦП, бит | Время преобразования, нс |

TRW | TDC 1014 | 6 | 30 |

TRW | TDC 1007j | 8 | 30 |

AMD | AM 6688 | 4 | 10 |

Весовой метод построения АЦП называют методом поразрядного уравновешивания или поразрядного взвешивания. Структурная схема этого АЦП приведена на рис. 1.26. Она содержит устройство выборки и хранения (УВХ); компаратор А1; источник опорного напряжения Uo, тактовый генератор Go ; цифро-аналоговый преобразователь; регистр последовательного приближения.

Рис. 1.26

При весовом методе построения АЦП - каждый разряд выходного кода получается за время одного цикла преобразования. Компаратор определяет, превышает ли входное напряжение АЦП напряжение пропорциональное коду старшего разряда ЦАП. В случае превышения в старший разряд регистра записывается логическая “1”, а в противном случае записывается сигнал логического “0”. Если в старший разряд была записана логическая “1”, то из входного напряжения вычитается опорное напряжение, соответствующее старшему разряду ЦАП. Остаток сравнивается с опорным напряжением, пропорциональным следующему разряду ЦАП, и т.д. Количество циклов преобразования весового АЦП равно количеству его разрядов.

Алгоритм работы регистра последовательного приближения АЦП поразрядного уравновешивания приведен на рис. 1.27. Точность преобразования АЦП поразрядного уравновешивания ограничена точностью изготовления резистивных матриц ЦАП. Характеристики интегральных АЦП поразрядного уравновешивания приведены в табл. 1.4. Погрешности аналого-цифрового преобразования определяются статическими и динамическими составляющими.

Рис. 1.27

Фирма изготовитель | Тип микросхемы | Разрядность АЦП, бит | Время преобразования, нс |

| К 572 ПВ2 | 12 | 110 |

| К 572 ПВ3 | 8 | 15 |

| К 572 ПВ4 | 8 | 32 |

| К 1108 ПВ1 | 10 | 0,9 |

| К 1113 ПВ1 | 10 | 30 |

TRW | TDC 100 lj | 8 | 0,4 |

TRW | TDC 1013j | 10 | 1 |

AD | AD 7574 | 8 | 15 |

AD | AD 7570 L | 10 | 20 |

AD | AD 574 | 12 | 25 |

Рис. 1.28

Наряду с систематической ошибкой квантования в АЦП имеют место аддитивная и мультипликативная составляющие погрешности преобразования. Градуировочные характеристики АЦП с учетом этих погрешностей приведены на рис. 1.29. Аддитивная погрешность преобразования обусловлена параллельным смещением градуировочной характеристики (смещение нуля) АЦП. Мультипликативная погрешность преобразования вызвана отклонением коэффициента чувствительности от характеристики идеального АЦП. Современные технологии с применением микропроцессоров позволяют существенно минимизировать эти погрешности с помощью периодической коррекции “нуля” и автоматической коррекции чувствительности. Поэтому не скомпенсированная часть аддитивной и мультипликативной составляющих погрешности, в первом приближении, может быть оценена как температурный дрейф этих величин между циклами коррекции работы АЦП.

Систематическая ошибка квантования в АЦП может привести к нелинейности градуировочной характеристики (рис. 1.30).

Рис. 1.30

Вторым видом нелинейности АЦП является дифференциальная нелинейность. Она показывает, насколько максимальная ширина отдельной ступеньки отличается от заданного значения z. Если эта величина превышает значение z, то при преобразовании некоторые числа выходного кода могут быть пропущены.

Динамическая погрешность АЦП определяется скоростью изменения входного сигнала и временем преобразования АЦП.

При преобразовании сигналов входное напряжение постоянно изменяется, а АЦП поразрядного уравновешивания преобразует зафиксированное значение входного напряжения, запомненное с помощью УВХ. Поэтому за время преобразования в АЦП входное напряжение изменяет своё значение на некоторую величину. Это изменение входного напряжения и является динамической погрешностью.

Наименьшее значение динамической погрешности обеспечивается при использовании параллельных АЦП.